- -52%

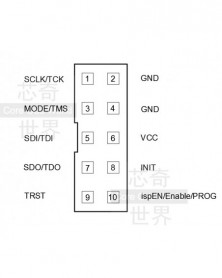

USB letöltési vonal letöltő HW-USBN-2A FPGA CPLD ISP szimulációs író

USB letöltési vonal letöltő HW-USBN-2A FPGA CPLD ISP szimulációs író

6 638 Ft

52% megtakarítás

13 829 Ft

Nincs adó

USB download line downloader HW-USBN-2A FPGA CPLD ISP simulation burner - Product features: 1.Lattice original design scheme is stable and reliable. 2. adopt current limiting and electrostatic protection to ensure full confidence. 3. suppor

Szállításii feltételek

Biztonsági feltételek

Visszaküldési feltételek